## **Fractional-N PLL Chipset Evaluation Kit**

Analog, Digital & Mixed-Signal ICs, Modules, Subsystems & Instrumentation

# User Manual

### Software & Hardware Installation

Order On-Line at: www.hittite.com Receive the latest product releases - click on "My Subscription"

20 Alpha Road Chelmsford, MA 01824 Phone: 978-250-3343 • Fax: 978-250-3373 • sales@hittite.com Part # **140-00055-00** Rev. A - v00.0811

ECN# CP111380

Rev. A - v00.0811

#### **Table of Contents**

| 1.      | Introduction                                                   |

|---------|----------------------------------------------------------------|

| 2.      | Package Contents                                               |

| 2.1     | Hardware                                                       |

| 2.2     | Software                                                       |

| 3.      | Operating Environment                                          |

| 4.      | Setup and Installation                                         |

| 4.1     | User Provided Equipment                                        |

| 4.2     | Software Installation                                          |

| 4.3     | Hardware Setup                                                 |

| 4.3.1   | Default Hardware Test Configuration                            |

| 4.3.2   | Loop Filter Configuration                                      |

| 4.3.2.1 | Default Loop Filter Configuration                              |

| 4.3.2.2 | User-Defined Loop Filter Configurations                        |

| 4.3.2.3 | Passive Loop Filter Configuration Example                      |

| 4.3.3   | Evaluating HMC983LP5E Fractional Divider as a Stand-Alone Part |

| 4.3.4   | Evaluating HMC984LP4E Phase Detector as a Stand-alone Part     |

| 5.      | Using the HMC983LP5E & HMC984LP4E Evaluation Software          |

| 5.1     | Launch Hittite Dual-Chip Synthesizer Software                  |

| 5.2     | Using the HMC983LP5E & HMC984LP4E Evaluation Software          |

| 5.3     | Load the register files                                        |

| 6.      | Synthesizer Programming                                        |

| 6.1     | Frequency Selection                                            |

| 6.2     | Frequency Step                                                 |

| 6.3     | Fractional/Integer Mode                                        |

| 6.4     | Check Lock                                                     |

| 6.5     | Register Read/Write                                            |

| 6.6     | Synthesizer Configuration Save/Load                            |

#### Notice

Hittite Microwave Corporation has prepared this manual for use by Hittite personnel and customers as a guide for the proper installation, operation, and maintenance of Hittite equipment and computer programs. The drawings, specifications, and information contained herein are the property of Hittite Microwave Corporation, and any unauthorized use or disclosure of these drawings, specifications, and information is prohibited; they shall not be reproduced, copied, or used in whole or in part as the basis for manufacture or sale of the equipment or software programs without the prior written consent of Hittite Microwave Corporation.

Rev. A - v00.0811

#### 1. Introduction

This document describes the functionality of the HMC983LP5E & HMC984LP4E Evaluation Kit, and provides high level instructions for using and configuring the Kit. The Kit includes PC compatible software with a Graphical User Interface (GUI) that allows the user to read from and write to all device registers and observe full functionality and performance of either the HMC983LP5E and/or the HMC984LP4E.

The HMC983LP5E & HMC984LP4E evaluation board included in the Kit is configured by default to form a complete frequency synthesizer. Hardware board changes are required to configure the HMC983LP5E & HMC984LP4E evaluation board to evaluate the HMC983LP5E (Fractional Divider), or the HMC984LP4E (Phase Detector) separately. Hardware configuration requirements are described in section <u>4.3</u>.

Note: For most up-to-date software download and information please visit www.hittite.com.

#### 2. Package Contents

#### 2.1 Hardware

Verify that all the items listed in Table 1 are included in the shipment.

| Item                                       | Quantity |

|--------------------------------------------|----------|

| HMC983LP5E & HMC984LP4E Evaluation Board   | 1        |

| USB Interface Board                        | 1        |

| 6' USB A Male to USB B Male Cable          | 1        |

| CD ROM (Contains User Manual and software) | 1        |

Table 1: Packing List

#### 2.2 Software

The HMC983LP5E & HMC984LP4E Evaluation Software enables users to communicate with and control HMC983LP5E & HMC984LP4E Evaluation Board with their PC, and observe full functionality and performance of the HMC983LP5E & HMC984LP4E.

#### 3. Operating Environment

This evaluation kit is designed for use in a laboratory setting at ambient room temperature (25 °C) and is not protected against moisture. The USB Interface Board has an ESD rating of +/-3000 V, however the HMC983LP5E & HMC984LP4E may have a lower rating (check the product's data sheet for its specific ESD rating). Use appropriate ESD procedures and precautionary measures when handling all electronic hardware.

Rev. A - v00.0811

#### 4. Setup and Installation

#### 4.1 User Provided Equipment

In addition to the items provided in the evaluation kit, the user must provide the following equipment to evaluate the HMC983LP5E & HMC984LP4E under test.

- DC Power Supply

- DC Cables

- Spectrum Analyzer

- Computer (PC) with Standard USB port

For detail specifications regarding operating system and software requirements please visit **www.hittite.com**

#### **4.2 Software Installation**

1. Double-click on the "Hittite Dual Chip Synth Eval Software Installer Vxxxx.exe" file available on the Evaluation Kit CD and/or downloaded from <u>www.hittite.com</u>, and follow the installation wizard.

#### 4.3 Hardware Setup

The HMC983LP5E & HMC984LP4E evaluation board includes both the Phase Detector (HMC984LP4E) and the Fractional Divider (HMC983LP5E) that are configured by default to together form a complete frequency synthesizer. Hardware board changes are required to configure the HMC983LP5E & HMC984LP4E evaluation board to evaluate the HMC983LP5E (Fractional Divider), or the HMC984LP4E (Phase Detector) separately. Hardware test configurations for testing the HMC983LP5E and HMC984LP4E separately are discussed in sections <u>4.3.2</u> and <u>4.3.3</u> respectively.

The default evaluation board configuration is shown in the HMC983LP5E & HMC984LP4E evaluation board schematic that is included in the HMC983LP5E & HMC984LP4E Evaluation Kit. The schematic also includes optional configurations. All components that are part of optional configurations are not populated on the HMC983LP5E & HMC984LP4E evaluation board, and are labeled as 'DEPOP' in the HMC983LP5E & HMC984LP4E evaluation board schematic. Components required for optional configuration are not included in the HMC983LP5E & HMC983LP5E & HMC984LP4E evaluation board schematic. Components required for optional configuration are not included in the HMC983LP5E & HMC984LP4E Evaluation Kit, and have to be supplied by the user.

#### 4.3.1 Default Hardware Test Configuration

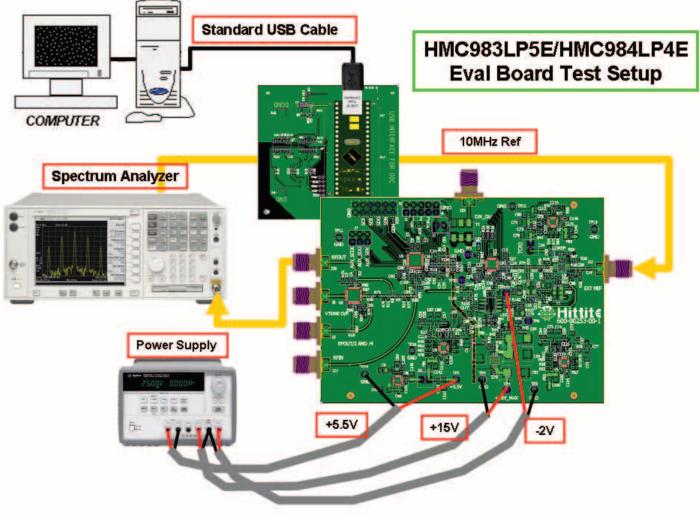

To evaluate both the HMC983LP5E and the HMC984LP4E together as a complete frequency synthesizer connect all hardware as shown in <u>Figure 1</u>.

Fractional-N PLL Chipset Evaluation Kit User Manual

Figure 1. Default Evaluation Board Test Setup

- 1. Plug the USB Interface Board header connector into the evaluation board header connector.

- 2. Connect the USB Interface Board to the USB port of the PC through the USB Cable provided in the Kit. The PC should then detect new hardware called DLP2332M.

- 3. Setup the evaluation board

- Ensure that Jumpers on J4 and J24 are installed.

- Connect the J28 (RFOUT SMA connector) of the HMC983LP5E & HMC984LP4E evaluation board output to a test instrument such as a spectrum analyzer.

- Connect the test instruments (Spectrum Analyzer's) 10 MHz Reference Output to J32 SMA connector (external reference input) of the HMC983LP5E & HMC984LP4E Evaluation Board.

- Set the DC power supply to +5.5 V and connect to the evaluation board. This supply is used to

power all of the components on the evaluation board except the AD797ARZ OpAmp used in the

active loop filter configuration.

- Set the DC power supply to +15 V and -2 V and connect to the evaluation board. This supply is used to power the AD797ARZ OpAmp used in the active loop filter configuration.

5

Rev. A - v00.0811

#### 4.3.2 Loop Filter Configuration

The HMC983LP5E & HMC984LP4E evaluation board allows both active and passive loop filter configurations.

#### 4.3.2.1 Default Loop Filter Configuration

The default configuration is an active loop filter using AD797ARZ OpAmp. Because the AD797ARZ is an inverting OpAmp, the provided default register setting files for the HMC984LP4E phase detector are configured for inverted phase polarity with offset current set in the up direction. It is recommended to change the HMC984LP4E phase detector polarity to non-inverting (Reg03h[4] = 0 of HMC984LP4E), and offset current direction to down (Reg04h[21] = 0 and Reg04h[22] = 1 of HMC984LP4E), when using non-inverting (active or passive) loop filter design.

#### 4.3.2.2 User-Defined Loop Filter Configurations

Hittite PLL Design software that is included in the HMC983LP5E & HMC984LP4E evaluation kit and available for download from <u>www.hittite.com</u> is recommended to be used to design user-defined loop filter configurations, if needed. The Hittite PLL Design model files for HMC983LP5E & HMC984LP4E evaluation board are available upon request by contacting apps-support@hittite.com.

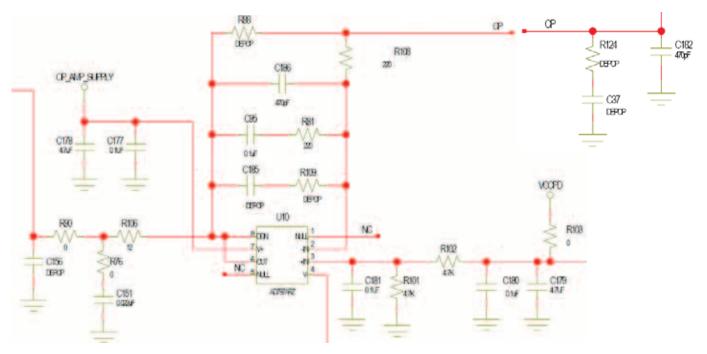

Hardware board changes are required to change the loop filter design or configuration. <u>Figure 2</u> shows all of the loop filter components present on the HMC983LP5E & HMC984LP4E evaluation board. More details are available in the HMC983LP5E & HMC984LP4E evaluation board schematic.

Rev. A - v00.0811

Figure 2. Dual Chip Synthesizer Loop Filter

#### 4.3.2.3 Passive Loop Filter Configuration Example

To configure the HMC983LP5E & HMC984LP4E evaluation board for a third order passive loop filter design with loop filter bandwidth of 118 kHz and 76 degree phase margin, the following components need to be removed:

• R108, C186, C95, R81

+15 V and -2 V power supply needs to be disabled.

The following component values need to be set (component details are shown in <u>Figure 2</u> and available in the HMC983LP5E & HMC984LP4E evaluation board schematic that is included in the HMC983LP5E & HMC984LP4E Evaluation Kit):

- C182 = 120 pF

- C37 = 47 nF

- C151 = 390 pF

- R124 = 300 Ω

- R88 = 0 Ω

- R106 = 120 Ω

- R76 = 0 Ω

Finally, the HMC984LP4E phase detector polarity needs to be set to non-inverting (Reg03h[4] = 0 of HMC984LP4E), and offset current direction set to down (Reg04h[21] = 0 and Reg04h[22] = 1 of HMC984LP4E). Detailed register writes required for these changes are available in the HMC984LP4E data sheet.

#### 4.3.3 Evaluating HMC983LP5E Fractional Divider as a Stand-Alone Part

Hardware board changes are required to configure the HMC983LP5E & HMC984LP4E evaluation board to test the HMC983LP5E as a stand-alone part. For the changes below please refer to the HMC983LP5E & HMC984LP4E evaluation board schematic.

The following components need to be depopulated:

• R10, R11, and R91

The following components (labeled 'DEPOP' in the HMC983LP5E & HMC984LP4E evaluation board schematic) need to be populated:

- R6 = R13 = 75 Ω

- R89 = 0 Ω

- C25 = C49 = 3300 pF

- J29 SMA Connector

- T2 Balun ADT2-1T

And jumpers J4 and J24 need to be removed.

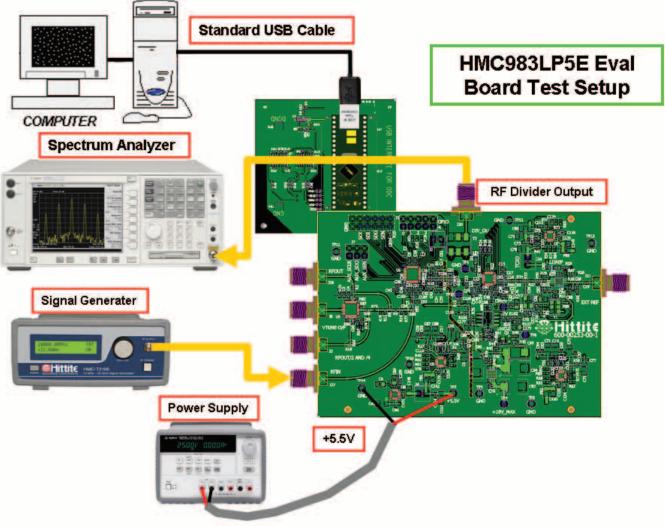

The measurement test setup for evaluating standalone HMC983LP5E is shown in Figure 3.

- 1. Plug the USB Interface Board header connector into the evaluation board header connector.

- 2. Connect the USB Interface Board to the USB port of the PC through the USB Cable provided in the kit. The PC should then detect new hardware called DLP2332M.

- 3. Setup the evaluation board

- Ensure that Jumpers on J4 and J24 are not installed.

- Connect the J29 (DIV\_OUT SMA connector) of the HMC983LP5E & HMC984LP4E evaluation board to a test instrument such as a spectrum analyzer.

- Supply the input signal to be divided to the J27 (RFIN SMA connector) of the HMC983LP5E & HMC984LP4E evaluation board.

- Set the DC power supply to +5.5 V and connect to the evaluation board. This supply is used to

power all of the components on the evaluation board except the AD797ARZ OpAmp used in the

active loop filter configuration.

Fractional-N PLL Chipset Evaluation Kit User Manual

Figure 3. Evaluation Board Test Setup For Testing Stand-Alone HMC983LP5E

#### 4.3.4 Evaluating HMC984LP4E Phase Detector as a Stand-alone Part

Hardware board changes are required to test the HMC984LP4E as a stand-alone part with a divider and/or a VCO other than the HMC983LP5E and the HMC507LP5E which are included in the HMC983LP5E & HMC984LP4E Evaluation Board.

To evaluate the HMC984LP4E as a stand-alone part, the following changes are required. Details are also available in the HMC983LP5E & HMC984LP4E evaluation board schematic.

The following components need to be depopulated:

• R133, and R134

The following components (labeled 'DEPOP' in the HMC983LP5E & HMC984LP4E evaluation board schematic) need to be populated:

- C25 = C49 = 3300 pF

- J29 SMA Connector

- T2 Balun ADT2-1T

Rev. A - v00.0811

Jumper J24 is required and jumper J4 has to be removed if on-board VCO HMC507LP5E is not needed. Using this setup the SMA connector J29 will be the input into the HMC984LP4E, and the output of the HMC984LP4E is available at SMA connector J5 (VTUNE O/P).

#### 5. Using the HMC983LP5E & HMC984LP4E Evaluation Software

#### 5.1 Launch Hittite Dual-Chip Synthesizer Software

Click on "Launch Hittite DualChip V1020.exe" from the Start, Program Files, Hittite Microwave Corp Windows menu.

#### 5.2 Using the HMC983LP5E & HMC984LP4E Evaluation Software

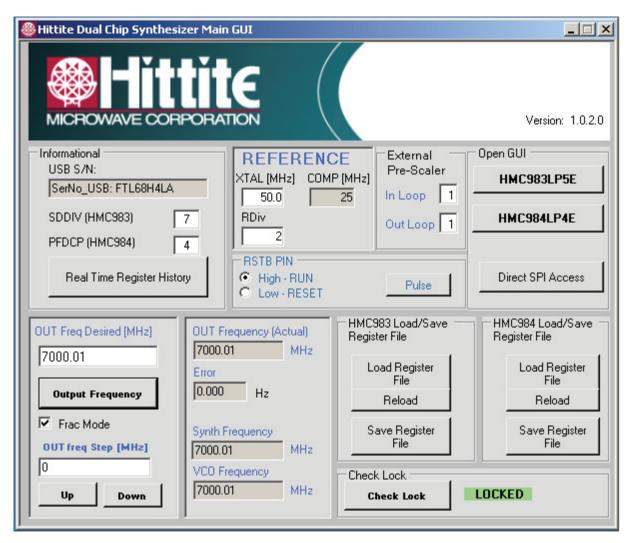

Hittite dual chip synthesizer product selection window shown in <u>Figure 4</u> will appear. From the drop down list, select HMC983LP5E & HMC984LP4E, as shown in <u>Figure 4</u>.

| 🍔 Hittite Dual Chip Synthesizer Evaluati 🔳 🗖 🔀                         |  |  |  |  |

|------------------------------------------------------------------------|--|--|--|--|

| WICROWAVE CORPORATION Version: 1.0.2.0                                 |  |  |  |  |

| Select Product From Drop Down List                                     |  |  |  |  |

| SDDIV Parts List<br>HMC983LP5E                                         |  |  |  |  |

| Product : HMC983LP5E<br>INIT PIN: RstB<br>INFORMATION : SDDIV (HMC983) |  |  |  |  |

| < <u>&gt;</u>                                                          |  |  |  |  |

| PFDCP Parts List<br>HMC984LP4E                                         |  |  |  |  |

| Product : HMC984LP4E<br>INIT PIN: RstB<br>INFORMATION : PFDCP (HMC984) |  |  |  |  |

| × ×                                                                    |  |  |  |  |

| Done Quit                                                              |  |  |  |  |

Figure 4. Hittite Dual Chip Synthesizer Product Selection Window

• Press "Done", the HMC983LP5E & HMC984LP4E Main Control GUI shown in Figure 5 will appear.

Rev. A - v00.0811

| 🛞 Hittite Dual Chip Synthesizer Main GUI |                                  |                            |                                   |  |  |  |  |  |

|------------------------------------------|----------------------------------|----------------------------|-----------------------------------|--|--|--|--|--|

| WICROWAVE CORPORATION Version: 1.0.2.0   |                                  |                            |                                   |  |  |  |  |  |

| Informational     USB S/N:               | REFERENCE                        | External<br>Pre-Scaler     | Open GUI                          |  |  |  |  |  |

| SerNo_USB: FTL68H4LA                     | XTAL [MHz] COMP                  | [MHz]                      | HMC983LP5E                        |  |  |  |  |  |

| SDDIV (HMC983)                           | 80.0                             | 50 In Loop 1<br>Out Loop 1 | HMC984LP4E                        |  |  |  |  |  |

| PFDCP (HMC984) 4                         |                                  |                            | <u></u>                           |  |  |  |  |  |

| Real Time Register History               | C High - RUN<br>C Low - RESET    | Pulse                      | Direct SPI Access                 |  |  |  |  |  |

|                                          | IUT Frequency (Actual) 10000 MHz | HMC983 Load/Save           | HMC984 Load/Save<br>Register File |  |  |  |  |  |

|                                          | irror                            | Load Register<br>File      | Load Register<br>File             |  |  |  |  |  |

| Output Frequency                         | D Hz                             | Reload                     | Reload                            |  |  |  |  |  |

|                                          | ynth Frequency MHz               | Save Register<br>File      | Save Register<br>File             |  |  |  |  |  |

|                                          | /CO Frequency<br>10000 MHz       | Check Lock<br>Check Lock   | UNLOCKED                          |  |  |  |  |  |

|                                          |                                  |                            |                                   |  |  |  |  |  |

Figure 5. Hittite Dual Chip Synthesizer Main GUI Dialog

#### 5.3 Load the register files.

- To load the default register files for the HMC983LP5E or HMC984LP4E, click on "Load Register File" button in the HMC983LP5E or HMC984LP4E Load/Save Register File frame which is located in the lower right corner of the display. Double-click on the Register Setting Files folder and select either the integer or fractional register file for the appropriate device (HMC983LP5E or HMC984LP4E), and press "Load Register File" button.

- Press the "Check Lock" button; The Check Lock should now display the green 'LOCKED' display indicator as shown in Figure 12.

Fractional-N PLL Chipset Evaluation Kit User Manual

Figure 6. Hittite Dual Chip Synthesizer Main GUI Indicating Synthesizer Lock State

#### 6. Synthesizer Programming

#### **6.1 Frequency Selection**

To program the synthesizer to a desired frequency, enter the desired frequency in the "OUT Freq Desired" box and press the "Output Frequency" button (Reference divider is only updated when the "Output Frequency" button is pressed). The "OUT Freq (Actual)" box displays the frequency that the synthesizer is generating. The "Error" box displays the frequency error between the desired and generated frequencies.

#### 6.2 Frequency Step

To step up/down in frequency, enter the desired frequency step size in MHz in the "OUT freq Step" window and press the "Up"/"Down" button.

Rev. A - v00.0811

#### 6.3 Fractional/Integer Mode

To operate in Fractional Mode, check the "Frac Mode" box, otherwise the synthesizer will operate in Integer Mode. The default register setting files included in the HMC983LP5E & HMC984LP4E evaluation software include both fractional and integer versions which are named correspondingly. If integer operation is desired, it is recommended to use integer register files, and vice-versa for fractional mode of operation.

#### 6.4 Check Lock

The "LOCKED"/"UNLOCKED" indicator is updated every time the "Update Frequency" button is pressed. The locked state can be confirmed at any time by pressing the "Check Lock" button.

#### 6.5 Register Read/Write

"Direct SPI Access" buttons provide direct register read/write capability in Hex and Decimal, enabling the user to configure each component in detail.

To observe all of the register states in detail simultaneously, click the appropriate HMC983LP5E or HMC984LP4E button in "Open GUI" frame of the "Hittite Dual Chip Synthesizer Main GUI" dialog (Figure 6). Depending on the selected part (HMC983LP5E or HMC984LP4E) Figure 7 or Figure 8 will appear. In the Detailed GUIs in Figure 7 and Figure 8 (for HMC983LP5E or HMC984LP4E respectively) each register is controlled by its own "Read" and "Write" button in its sub-panel. Changes made by clicking on any check box are only implemented after clicking that register's "Write" button. Similarly the data is only updated after the "Read" button is clicked.

#### Fractional-N PLL Chipset Evaluation Kit User Manual

| #MC983LP5E                                |                                             |                                                   |                                                        |

|-------------------------------------------|---------------------------------------------|---------------------------------------------------|--------------------------------------------------------|

|                                           | Reg 05H: Integer Set-Point/Trig Delay       | Reg 0EH: SD Modulator Configuration               | Regs 12H 13H: Ramp Step Size Symm or Up                |

|                                           | 280 Read                                    | 10: MASH111 [1:0] Modulator                       | dec                                                    |

| Reg 00H: Chip ID, Soft Reset, Read        | Integer Divsion Ratio [19:0]d Write         | 2: Ramp Auto Repeat Force from SPI                | To Hex To Frac Read                                    |

| Soft Reset                                | Regs 06H 7H: Frac Set-Point/Dn Dwell        | 3: Ramp Auto Repeat En via SPI                    | <lsb 18'=""> Write</lsb>                               |

|                                           | dec                                         | 111: Automatic [6:4] Delay Line Intg              | < <u>MSB 30'&gt;</u> C3B 10?                           |

| 97330 Chip ID [hex] Read                  | To Hex To Frac Read                         | O8: Autoseed Mode                                 | Reg 12H Reg 13H                                        |

| Reg 01H: Settings                         | <msb 30'=""> <lsb 18'=""> Write</lsb></msb> | 09: Reserved                                      |                                                        |

| 00: VCO Buffer Enable                     | 68DB8 2EB20                                 | 10: Coh Freq Hop Mode     11: Ramp Mode           | Regs 14H 15H: Ramp NSTEP Symm or Up                    |

| 01: Reserved                              | Reg 6H Reg 7H                               | 12: Ramp Start From SPI                           | dec                                                    |

| 02: AUX SPI Enable                        | Reg 08H: GPIO Configuration                 | 13: Ramp Ext Start En                             | To Hex To Dec Read                                     |

| ✓ 03: Sigma Delta Enable                  | 0000:  (3:0) GPO Select                     | 14: Bypass All<br>15 [18:15] CSP Step             | <msb 30'=""> <lsb 18'=""> Write</lsb></msb>            |

| O4: GPIO Enable                           | 0 [8:4] GPO Test                            |                                                   | 0 0                                                    |

| Ø5: RF Divider Enable                     | 31 [13:9] GPO Pin En                        | ☐ 19: Ext Seq Sel<br>☐ 20: Ext Seq Fe Sel         | Reg 14H Reg 15H                                        |

| 06: Output buffer Enable                  |                                             | 🔲 21: Trigg Ext Start En                          | Reg 16H: DSM Configuration                             |

|                                           | Reg 09H: HMC984 Chip Address (Local)        | ☑ 22: Ramp Symmetrical Up_Dn                      | 00: 48 bits [1:0] LSB Ctrl Acc0                        |

| 08: PSCLK to Digital Enable               | 2 Write Read                                | 23: Intg New Lock Strobe     24: Ramp Single Step |                                                        |

|                                           |                                             | 25: Ramp Single Dir                               | 00: 48 bits [3:2] LSB Ctrl Acc1                        |

| Read                                      | Regs: 0AH 0BH SD Modulator Seed             | Z6: Ramp Start Up_Dn_B     Read     Read          | 00: 48 bits [5:4] LSB Ctrl Acc2                        |

| 2 dec [13:0] Write                        |                                             | 🔲 28: Trigg Ext Phase Adj 🛛 🛛 🗤 🖉                 | 000: 🗾 [8:6] disable Acc Frac Clk                      |

| Reg 03H: AUX SPI Register                 | To Hex To Frac Read                         | 29: CSP Step x16                                  | 000: [11:9] Disable Acc Intg Clk                       |

| 0 Read                                    | <msb 30'=""> <lsb 18'=""> Write</lsb></msb> | Reg 0FH: VCO Divider Configuration                | 12: disable_3ff_clk                                    |

| <4 bits address> <9 bits data> Write      | 4241 10081                                  | 01: Duty Cyc Wide                                 | 13: disable_mash_clk                                   |

| Reg 04H: AUX SPI Setting                  | Reg 0AH Reg BH                              | 011: 12.5mA 💌 [4:2] bias Write                    | 14: disable_postfilter_clk                             |

| 0 [2:0] AUX Chip Address                  | dec                                         | 05: Reset RF Divider                              | 15: disable_intgdlyline_clk     16: disable_inpbuf_clk |

| 03: AUX SPI Clk div by4( 1 = En div by 4) |                                             | 3 [8:6] Divider Resynch Bias Select               | 17: disable_outbuf_clk     Read                        |

|                                           | To Hex To Dec Read                          | 1 [11:9] RF Buffer Bias Select                    | 18: disable_cohop_clk     Write                        |

| 15: Keep Gate Clk Xtal On                 | <msb 30'=""> <lsb 18'=""> Write</lsb></msb> | [14:12] Divider Pulsewidth select                 | 19: disable_ramp_clk                                   |

| Write                                     |                                             |                                                   | Regs: 19H 1AH Ramp Down Step Size                      |

|                                           | Reg CH Reg DH                               | Regs 10H 11H: Ramp DWELL Symm or Up               | dec                                                    |

| 0                                         | in CUI                                      |                                                   | To Hex To Frac Read                                    |

| Open Ma                                   | indor                                       | To Hex To Dec Read                                | ) utile                                                |

|                                           |                                             | <msb 30'=""> <lsb 18'=""> Write</lsb></msb>       | <msb 30'=""> <lsb 18'=""></lsb></msb>                  |

| Read All and                              | d Update                                    |                                                   | Reg 19H Reg 1AH                                        |

|                                           |                                             | Reg 10H Reg 11H                                   | ring for                                               |

Figure 7. HMC983LP5E Detailed GUI

Rev. A - v00.0811

|                                                                                     | Register 03H: PFD Register                                                   | Register 06H: LKD_M (Lock Detect) Register |  |  |  |  |  |

|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------|--------------------------------------------|--|--|--|--|--|

|                                                                                     | 4 PFD Sat RSTB Delay [2:0]                                                   | 127 [6:0] LKD Duration Thr Hi              |  |  |  |  |  |

| Register 00H: Chip ID, Soft Reset                                                   | <ul> <li>✓ 03: PFD SAT Auto Disable</li> <li>✓ 04: PFD Swap Phase</li> </ul> | 0 [13:7] LKD Duration Thr Lo               |  |  |  |  |  |

| Soft Reset                                                                          | □ 05: PFD Short Mode                                                         | 512 [23:14] LKD Count Ok Thr               |  |  |  |  |  |

|                                                                                     | 06: PFD Up Enable                                                            | Read Write                                 |  |  |  |  |  |

| 97331 Chip ID [hex] Read                                                            | 07: PFD Dn Enable     08: PFD Force Up                                       |                                            |  |  |  |  |  |

| Register 01H: Enable Register                                                       | O9: PFD Force Dn     Read                                                    | Register 07H: LKDOS(Lock Detect) Register  |  |  |  |  |  |

| 00: Use SPICE                                                                       | 10: PFD LD To Dig En Write                                                   | 4096 LKDOS Win Count Max [15:0]            |  |  |  |  |  |

| ✓ 01: SPI CE                                                                        | I1: PFD RST When Xtal Gate                                                   | 100: LKDOS One Shot[18:16]                 |  |  |  |  |  |

| 02: Rdiv Enable     03: PED Enable                                                  | Register 04H: Charge Pump Register                                           | 00: Fastest  LKDOS Ring OSC [20:19]        |  |  |  |  |  |

| O3: PFD Enable     O4: PFDSAT Enable                                                | 2.54 mA [6:0] CP UP Current                                                  | 21: Ring OSC Mode Read                     |  |  |  |  |  |

| 05: CP Enable                                                                       | 2.54 mA [13:7] CP DN Current                                                 | ✓ 22: Ring OSC One Shot                    |  |  |  |  |  |

| O6: Lock Detect enable                                                              | 245 uA 🗾 [20:14] Offset Current                                              | Write                                      |  |  |  |  |  |

| 07: Lock Detect Watch Dog     08: Legacy Lock Detect enable                         | Z1: Up Offset Current     Read                                               | Register 08H: GPIO Register                |  |  |  |  |  |

| 09: GPIO Output Enable                                                              | 22: Down Offset Current     23: High Gain Mode Enable     Write              | 0000: gpo_test. 💌 GPO Select[3:0]          |  |  |  |  |  |

| <ul> <li>✓ 10: Enable Reference Buffer</li> <li>✓ 11: Enable test clocks</li> </ul> | 00: 540uA 🔽 [25:24] Op-Amp Bias                                              | 0 GPO Test [5:4] Read                      |  |  |  |  |  |

| <ul> <li>✓ T1: Bias Enable</li> </ul>                                               | 26: CP Force Up Enable                                                       | 3 GPO Pin En[7:6] Write                    |  |  |  |  |  |

| I 3: PFD Sat Out Enable                                                             | 27: CP Force Down Enable                                                     | Register 09H: Reference Divider Settings   |  |  |  |  |  |

| 14: CP OP-AMP Enable      15: Spare                                                 | 28: CP Force Mid Rail Enable     29: Ring Oscillator Output to CP Enable     | 1 HMC983 Chip Addr Local [2:0] Read        |  |  |  |  |  |

| I6: Spare     Bead                                                                  | Register 05H: LKD FLXCPGAIN (LD) Register                                    | 03: Rdiv Bypass Force Write                |  |  |  |  |  |

| I 19: Cll. \/dia Buffer En                                                          | O0: LKD Win Asym En                                                          | Register 0AH: Spare                        |  |  |  |  |  |

| 19: Unused                                                                          | 01:LKD Win Asym Up                                                           | 10: Xtal DisSat Protection Read            |  |  |  |  |  |

|                                                                                     | D 02: LKD Be Bdiv                                                            | 11: Xtal High Freq Mode                    |  |  |  |  |  |

| Register 02H: Reference Divider Read                                                | 00: Disabled                                                                 | Register 10H: MEAS_REF Read Only           |  |  |  |  |  |

| 2 dec [13:0] Write                                                                  | Fix CP Mode Sel [4:3]                                                        | 340 Duration Ref [19:0]                    |  |  |  |  |  |

|                                                                                     | Register 12H: STATUS Read Only Register                                      | 20: Duration Ref Overflow                  |  |  |  |  |  |

| Read All and Update                                                                 | 00: Sign PFD(0 -> VCO Div Leading)                                           | Register 11H: MEAS_PFD Read Only Register  |  |  |  |  |  |

|                                                                                     | 🔽 01: Locked m_Test                                                          |                                            |  |  |  |  |  |

| Open Main GUI                                                                       | 02:llocked One Shot test                                                     | 38 Duration PFD [19:0]                     |  |  |  |  |  |

| l                                                                                   |                                                                              | 20: Duration PFD Overflow                  |  |  |  |  |  |

Figure 8. HMC983LP5E Detailed GUI

#### 6.6 Synthesizer Configuration Save/Load

To save a synthesizer configuration to a file, use the "Save Reg File" button in the bottom right corner of the main GUI shown as <u>Figure 6</u>. This functionality allows users to save and recall the desired synthesizer configuration state by using the "Load Reg File".

#### **Technical Support**

Please contact <u>apps-support@hittite.com</u> for any questions. Hittite Microwave provides local direct support in many areas around the world. Please see the "Contact Us" page at <u>www.hittite.com</u>.

Order On-Line at: www.hittite.com Receive the latest product releases - click on "My Subscription"

20 Alpha Road Chelmsford, MA 01824 Phone: 978-250-3343 • Fax: 978-250-3373 • sales@hittite.com